PUBLISHED BY INSTITUTE OF PHYSICS PUBLISHING AND SISSA

RECEIVED: December 11, 2007 ACCEPTED: February 26, 2008 PUBLISHED: March 27, 2008

# Design and implementation of the Front End Board for the readout of the ATLAS liquid argon calorimeters

N.J. Buchanan,<sup>*a*,1</sup> L. Chen,<sup>*a*,2</sup> D.M. Gingrich,<sup>*a*,3</sup> S. Liu,<sup>*a*</sup> H. Chen,<sup>*b*</sup> J. Farrell,<sup>*b*</sup> J. Kierstead,<sup>b</sup> F. Lanni,<sup>b</sup> D. Lissauer,<sup>b</sup> H. Ma,<sup>b</sup> D. Makowiecki,<sup>b</sup> V. Radeka,<sup>b</sup> S. Rescia,<sup>b</sup> H. Takai,<sup>b</sup> H. Ghazlane,<sup>c</sup> A. Hoummada,<sup>c</sup> H.G. Wilkens,<sup>d</sup> J. Ban,<sup>e,4</sup> S. Boettcher,<sup>e,5</sup> G. Brooijmans,<sup>e</sup> C.-Y. Chi,<sup>e</sup> S. Caughron,<sup>e</sup> M. Cooke,<sup>e</sup> D. Dannheim,<sup>e,6</sup> A. Gara,<sup>e,7</sup> A. Haas,<sup>e</sup> I. Katsanos,<sup>e</sup> J.A. Parsons,<sup>e</sup>\* S. Simion,<sup>e,8</sup> W. Sippach,<sup>e</sup> L. Zhang,<sup>e</sup> N. Zhou,<sup>e</sup> E. Ladygin,<sup>f</sup> E. Auge,<sup>g</sup> R. Bernier,<sup>g</sup> M. Bouchel,<sup>g</sup> A. Bozzone,<sup>g</sup> D. Breton,<sup>g</sup> C. de la Taille,<sup>g</sup> I. Falleau,<sup>g</sup> P. Imbert,<sup>g</sup> G. Martin-Chassard,<sup>g</sup> A. Perus,<sup>g</sup> J.P. Richer,<sup>g,9</sup> V. Tocut,<sup>g</sup> J-J. Veillet,<sup>g</sup> D. Zerwas,<sup>g</sup> F. Hubaut,<sup>h,10</sup> B. Laforge,<sup>h</sup> O. Le Dortz,<sup>h</sup> D. Martin,<sup>h</sup> Ph. Schwemling,<sup>h</sup> J. Collot,<sup>i</sup> D. Dzahini,<sup>i</sup> M.-L. Gallin-Martel,<sup>*i*</sup> P. Martin,<sup>*i*</sup> W.D. Cwienk,<sup>*j*</sup> J. Fent,<sup>*j*</sup> L. Kurchaninov,<sup>*j*,11</sup> G. Battistoni,<sup>k</sup> L. Carminati,<sup>k</sup> M. Citterio,<sup>k</sup> W. Cleland,<sup>1</sup> B. Liu,<sup>1</sup> J. Rabel,<sup>1</sup> G. Zuk,<sup>1</sup> K. Benslama,<sup>m</sup> E. Delagnes,<sup>n</sup> B. Mansoulié,<sup>n</sup> J. Teiger,<sup>n</sup> B. Dinkespiler,<sup>o,10</sup> T. Liu,<sup>o</sup> R. Stroynowski,<sup>o</sup> C.-A. Yang,<sup>o</sup> J. Ye,<sup>o</sup> M.L. Chu,<sup>p</sup> S.-C. Lee<sup>p</sup> and P.K. Teng<sup>p</sup> <sup>a</sup>Centre for Particle Physics, Department of Physics, University of Alberta, Edmonton, Alberta, Canada <sup>b</sup>Brookhaven National Laboratory (BNL), Upton, NY, U.S.A. <sup>c</sup>Faculté des Sciences, University of Casablanca, Casablanca, Morocco <sup>d</sup>CERN, Geneva, Switzerland <sup>e</sup>Columbia University, Nevis Laboratories, Irvington, NY, U.S.A. <sup>f</sup> Joint Institute for Nuclear Research, Dubna, Russia <sup>g</sup>Laboratoire de l'Accélérateur Linéaire (LAL), Orsay, France <sup>h</sup>LPNHE, Université Pierre et Marie Curie Paris 6, Université Denis Diderot Paris 7, CNRS/IN2P3, Paris, France <sup>i</sup>LPSC, Université Joseph Fourier Grenoble 1, CNRS/IN2P3, Institut National Polytechnique de Grenoble, Grenoble, France <sup>j</sup>Max-Planck-Institut für Physik, Werner-Heisenberg-Institut, Munich, Germany <sup>k</sup>Dipartimento di Fisica dell'Università di Milano and INFN, Milano, Italy <sup>1</sup>University of Pittsburgh, Pittsburgh, Pennsylvania, U.S.A. <sup>m</sup>University of Regina, Regina, Saskatchewan, Canada <sup>n</sup>CEA, DSM/DAPNIA, Centre d'Etudes de Saclay, Gif-sur-Yvette, France <sup>o</sup>Southern Methodist University, Dallas, Texas, U.S.A. <sup>*p*</sup>*Institute of Physics, Academia Sinica, Nankang, Taipei, Taiwan, R.O.C.*

<sup>1</sup>Now at Department of Physics, Florida State University, Tallahassee, Florida, U.S.A.

<sup>2</sup>Now at Department of Electrical and Computer Engineering, University of Saskatchewan, Saskatoon, Saskatchewan, Canada

<sup>3</sup>Also at TRIUMF, Vancouver, British Columbia, Canada

<sup>4</sup>Also at Institute of Experimental Physics, Kosice, Slovakia

<sup>5</sup>Now at Christian Albrechts University, Institute for Experimental and Applied Physics, Kiel, Germany

<sup>6</sup>Now at CERN

<sup>7</sup>Now at IBM T.J. Watson Research Center, USA

<sup>8</sup>Now at LAL

<sup>9</sup>Now at CPPM

<sup>11</sup>Now at TRIUMF *e\_mail:* parsons@nevis.columbia.edu

ABSTRACT: The ATLAS detector has been designed for operation at CERN's Large Hadron Collider. ATLAS includes a complex system of liquid argon calorimeters. The electronics for amplifying, shaping, sampling, pipelining, and digitizing the calorimeter signals is implemented on the Front End Boards (FEBs). This paper describes the design, implementation and production of the FEBs and presents measurement results from testing performed at several stages during the production process.

KEYWORDS: Calorimeters; Electronic detector readout concepts (gas, liquid).

<sup>\*</sup>Corresponding author.

# Contents

| 1.  | Introduction                                              | 2  |

|-----|-----------------------------------------------------------|----|

| 2.  | FEB specifications                                        | 3  |

| 3.  | Overview of the FEB architecture                          | 6  |

| 4.  | Analog Signal Processing                                  | 8  |

|     | 4.1 Preamplifiers                                         | 8  |

|     | 4.2 Hadronic Endcap Preshapers                            | 10 |

|     | 4.3 Shaper                                                | 12 |

|     | 4.4 SCA analog pipeline                                   | 13 |

|     | 4.5 Digitization and Gain Selection                       | 17 |

| 5.  | SCA Controller and FEB Digital Control                    | 19 |

| 6.  | SCA control and Address Bus                               | 21 |

| 7.  | Output optical link                                       | 22 |

| 8.  | FEB output data format                                    | 23 |

| 9.  | Level 1 Trigger Summing                                   | 26 |

| 10. | FEB Control Interfaces                                    | 29 |

|     | 10.1 Trigger and Timing Control                           | 29 |

|     | 10.2 Clock distribution                                   | 30 |

|     | 10.3 Configuration and slow control                       | 31 |

| 11. | FEB power distribution and monitoring                     | 32 |

| 12. | FEB layout and topology                                   | 33 |

| 13. | FEB production                                            | 36 |

| 14. | FEB testing                                               | 38 |

|     | 14.1 Initial test and highly accelerated stress screening | 38 |

|     | 14.2 Digital test                                         | 39 |

|     | 14.3 Analog test                                          | 42 |

| 15. | Performance of the FEB                                    | 45 |

#### 16. Summary

# 1. Introduction

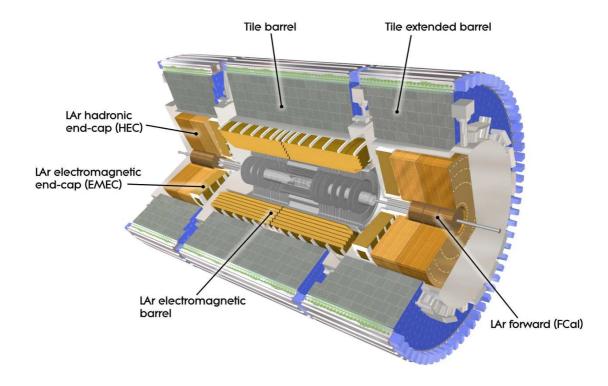

ATLAS [1] is a large general-purpose detector designed for operation at the Large Hadron Collider (LHC) at CERN. The LHC is a proton-proton collider which will operate with a center-of-mass energy of 14 TeV. A system of liquid argon (LAr) calorimeters forms one of the major ATLAS detector systems (see figure 1). The LAr calorimeters include the electromagnetic barrel (EMB) calorimeter, which is housed in the central cryostat and provides coverage for pseudorapidities  $|\eta| < 1.5$ . The ranges of larger pseudorapidity are covered by endcap calorimeter (EC) systems, housed in separate endcap cryostats. Each EC cryostat includes an electromagnetic endcap (EMEC) calorimeter, a hadronic endcap (HEC) calorimeter, and a forward calorimeter (FCAL) providing coverage up to  $|\eta| = 4.9$ . More details about the design, construction, and performance of the LAr calorimeters themselves can be found in Reference [2].

The electronic readout of the ATLAS LAr calorimeters is divided into a Front End (FE) system of boards mounted in custom crates directly on the cryostat feedthroughs, and a Back End (BE) system of VME-based boards located in an off-detector underground counting house. The FE system includes Front End Boards (FEB), which perform the readout and digitization of the calorimeter

**Figure 1.** Cut-away view of the ATLAS calorimeters. The LAr calorimeters are seen inside the scintillatorbased Tile hadronic calorimeters.

| Channel          | Total Active Channels   | 182,468                     |  |  |

|------------------|-------------------------|-----------------------------|--|--|

| count            | Number of FEBs          | 1524                        |  |  |

|                  | Channel density         | 128 channels/FEB            |  |  |

|                  | Power consumption       | pprox 0.7 W/channel         |  |  |

| Signal           | Sampling frequency      | 40 MHz                      |  |  |

| sampling         | L1 trigger latency      | < 2.5 µs (100 b.c.)         |  |  |

|                  | Max. L1 trigger rate    | 75 kHz                      |  |  |

|                  | Samples to read/channel | Typically 5, Maximum 32     |  |  |

|                  | Deadtime                | < few %                     |  |  |

| Energy           | Dynamic range           | $\approx 17$ bits           |  |  |

| measurement      | Calibration uncertainty | < 0.25%                     |  |  |

|                  | Noise/channel           | pprox 10 - 50 MeV           |  |  |

|                  | Coherent noise/channel  | < 5% of total noise/channel |  |  |

| Time measurement | Resolution              | < 100 ps                    |  |  |

| Trigger sums     | Gain uniformity         | < 5%                        |  |  |

**Table 1.** A summary of some of the main specifications of the ATLAS LAr Front End Board.

signals, Calibration boards which inject precision calibration signals, boards for producing analog sums for the Level 1 (L1) trigger, and other control and monitoring boards. The BE electronics includes Readout Driver (ROD) boards which perform DSP-based digital filtering of the signals.

A more detailed overview of the entire ATLAS LAr readout chain, and details of the BE system, can be found in Reference [3]. The overall FE system architecture is documented in Reference [4]. The purpose of this note is to describe the design and implementation of the ATLAS LAr FEB, including some information on the standalone performance of the FEB. The overall system performance of the ATLAS LAr readout electronics will be documented in a subsequent publication.

# 2. FEB specifications

The electronic readout of the ATLAS LAr calorimeters faces demanding specifications, a summary of which is provided in table 1. Given the fine segmentation of the ATLAS LAr calorimeters, a total of 182468 active channels must be read out. These are distributed among the EMB (60%), EMEC (35%), HEC (3%) and FCAL (2%). For noise optimization, the FEBs are placed in crates mounted directly on the calorimeter cryostat feedthroughs. A channel density of 128 channels per FEB is required to satisfy the space constraints of this on-detector location. With this density, and given the cabling of the calorimeters, a total of 1524 FEBs is required to read out the LAr calorimeters. Any heat dissipated by the electronics must be removed in order to not impact other detector subsystems. Therefore, maintaining a low power consumption, well below 1 Watt per channel, is important. Furthermore, since convective air cooling using fans cannot be used in this region of the detector, the FEBs are conductively cooled using an under-pressure water cooling system.

The FEBs must sample the LAr calorimeter signals at the LHC bunch crossing frequency of 40 MHz. The online selection of events is performed by the three-layered ATLAS trigger system [5]. In the first step, the L1 trigger uses partial information from the calorimeters and the muon system to reduce the trigger rate to a maximum L1 Accept rate of 75 kHz. For each L1 trigger, the FEB readout of typically five samples per channel must be accomplished with little deadtime, and the full event data made available for subsequent evaluation by the Level 2 and Level 3 trigger systems. The L1 trigger decision is performed by a deadtimeless, synchronous pipelined system with fixed latency of up to 2.5  $\mu$ s (100 bunch crossings), during which the FEB must store the time-sampled calorimeter signals. The FEB must be able, at lower trigger rates, to read out up to 32 samples per channel, in order to measure the entire waveform when desired during calibration or other special runs.

The energy resolution of the ATLAS electromagnetic (EM) calorimeters for EM showers is given by  $\sigma(E)/E \approx 10\%/\sqrt{E} \oplus 0.7\%/E$ , with the energy *E* is expressed in GeV and  $\oplus$  representing addition in quadrature. The resolution at high energies is dominated by the second, so-called constant, term, which arises due to a variety of contributions, including mechanical tolerances and variations in the calorimeter construction, time variations of the detector response, and uncertainties in the calibration. Achieving the goal of 0.7% for the constant term requires that the calibration of the readout is understood at a level of better than 0.25%.

For low energies, the noise contribution is also important. The noise for an electron shower in the EMB at low pseudorapidity is expected to be 190 MeV. Depending on the section of the calorimeter, the noise of the preamp loaded by the detector capacitance for a single calorimeter channel is typically  $\approx 10$  - 50 MeV. The low end of the FEB dynamic range is set by the requirement that the FEB noise be dominated by the preamp noise. The high end of the scale has been set to  $\approx$ 3 TeV, the largest energy that could be deposited in a single channel of the EM calorimeter due to an electron originating from the decay of a 5 TeV Z' boson. Being able to cover this entire energy range requires the FEB have a dynamic range of  $\approx 17$  bits.

Given the fine granularity of the calorimeter, the energy of an EM shower is obtained by summing the signals of typically 50-100 calorimeter cells; even more channels must be summed for a typical jet or for more global quantities such as missing transverse energy (MET). As a result, any coherent component of the noise is particularly critical. By studying the impact on the reconstruction, using MET, of a heavy SUSY Higgs boson decaying to tau pairs [6], a requirement has been set that the coherent noise per channel be less than 5% of the total noise per channel.

In addition to measuring the deposited energy per channel, the FEB readout must provide a measurement of the time of the deposition and also a  $\chi^2$ -type quantity related to how well the pulse shape follows the expected shape. Digital processing can be performed of the typically five time samples read out per channel to produce optimized measures of energy, time, and  $\chi^2$ . The  $\chi^2$  measurement provides sensitivity to pulses which are mismeasured due to waveform distortions produced by large energy depositions in neighboring bunch crossings. The time measurement provides, first of all, identification of the bunch crossing to which the energy deposit belongs. A timing resolution of  $\approx 5$  ns would be sufficient for this purpose given the time separation of 25 ns between subsequent bunch crossings. However, the calorimeter has a much better intrinsic timing resolution, and there are physics arguments to aim for excellent timing resolution. For example, some variants of Gauge Mediated Supersymmetry Breaking (GMSB) models imply existence of

|      | Radiation                          | Estimated            | DMILL                | Commercial Process   |

|------|------------------------------------|----------------------|----------------------|----------------------|

| Туре | Units                              | Level                | RTC                  | RTC                  |

| TID  | Gy                                 | 50                   | 525                  | 1700                 |

| NIEL | 1 MeV equiv. n/cm <sup>2</sup>     | $1.6 \times 10^{12}$ | $1.6 \times 10^{13}$ | $1.6 \times 10^{13}$ |

| SEE  | Hadrons (> 20 MeV)/cm <sup>2</sup> | $7.7 	imes 10^{11}$  | $7.7 	imes 10^{12}$  | $7.7 \times 10^{12}$ |

Table 2. Radiation levels for which FEB components had to be qualified. For more details, see the text.

a heavy gaugino which would decay to an undetected Graviton and a photon which, due to the finite lifetime of the gaugino, would hit the calorimeter with a slight delay and from an angle not directed to the primary vertex. A study [6] of such a scenario demonstrated that the pointing resolution of the calorimeter would be a powerful tool to identify such "non-pointing" photons, and a timing resolution much better than the mean delay of  $\approx 2$  ns would be helpful in confirming this signature. For large pulses, a timing resolution better than 100 ps should be achievable. Such a performance would also allow the possibility to use timing to help select the proper vertex in Higgs decays to a pair of photons, and to achieve some rejection of "pile-up" due to other proton-proton scatters within the same bunch crossing.

Due to their on-detector location, the FEBs must be able to tolerate significant levels of radiation. Simulations of the expected radiation field [7] predict that, during 10 years of LHC operation at design luminosity, the FEBs will experience a total ionizing dose (TID) of 5 kRad and nonionizing energy loss (NIEL) effects due to an equivalent fluence of  $1.6 \times 10^{12}$  1-MeV-neutrons/cm<sup>2</sup>. In addition, the possibility of single event effects (SEE), including single event upsets (SEU) of logic states, must be considered, given the exposure to  $7.7 \times 10^{11}$  hadrons/cm<sup>2</sup> with energies above 20 MeV. As will be described in a subsequent publication, all FEB components were subjected to an extensive radiation tolerance qualification process, with the required tolerance specified by multiplying these expected radiation levels by three safety factors (SF) which aim to account for uncertainties in the simulated radiation levels, for possible low dose rate effects, and for variations in radiation tolerance from lot to lot in production of an ASIC.

The radiation tolerance issues led to the development of a number of custom ASICs in specialized, radiation-tolerant semiconductor processes, and to a very limited use of "commercial-off-theshelf" (COTS) components. A number of ASICs were developed in the DMILL process [8], and several more using a commercial 0.25  $\mu$ m "deep submicron" (DSM) process, but using a special library which was radiation hardened through the use of a custom-developed enclosed transistor geometry [9]. The SF values were lower for the DMILL process, which was guaranteed by the vendor to be radiation tolerant, than for COTS components or ASICs produced in a commercial process that does not guarantee radiation tolerance. Table 2 summarizes the expected radiation levels as well as the "Radiation Tolerance Criteria" (RTC) values to which DMILL and other components had to be tested and qualified. The RTC values for commercial processes take into account the fact that the final production parts were purchased from known, homogeneous lots; otherwise, each of the commercial RTC values would have been an additional factor of two higher.

The on-detector location of the FEBs implies that there is no access to them during operation of the LHC, and gaining access requires a shutdown of considerable length. In particular, the FEBs

of the EMB detector are mounted in crates at either end of the barrel cryostat. Accessing these crates to repair or replace the FEBs requires rearranging or extracting large detector elements in the endcap regions, including the endcap calorimeter cryostats. While it is foreseen to access these crates once per year, during the long annual shutdown planned for the LHC, other opportunities for access will be very limited. Given these access difficulties, reliability is a key concern.

The limited use of COTS components, and reliance on specialized radiation-tolerant semiconductor processes, implies that very little is known about the expected lifetime of the individual components. All components were purchased with  $\approx$  (5-8)% spares, to allow for repairs. As is often the case for high energy physics instrumentation, essentially all FEB components are already obsolete and unavailable, so procurement or production of additional spares is not feasible. This fact, plus the current planning to upgrade the luminosity of the LHC in the future and extend even further its expected operations phase, makes the FEB lifetime issue even more critical. An accelerated lifetime test is being performed by operating a number of pre-production FEBs at elevated temperature in an environmental chamber. Results of this test, once available, will be reported in a subsequent publication.

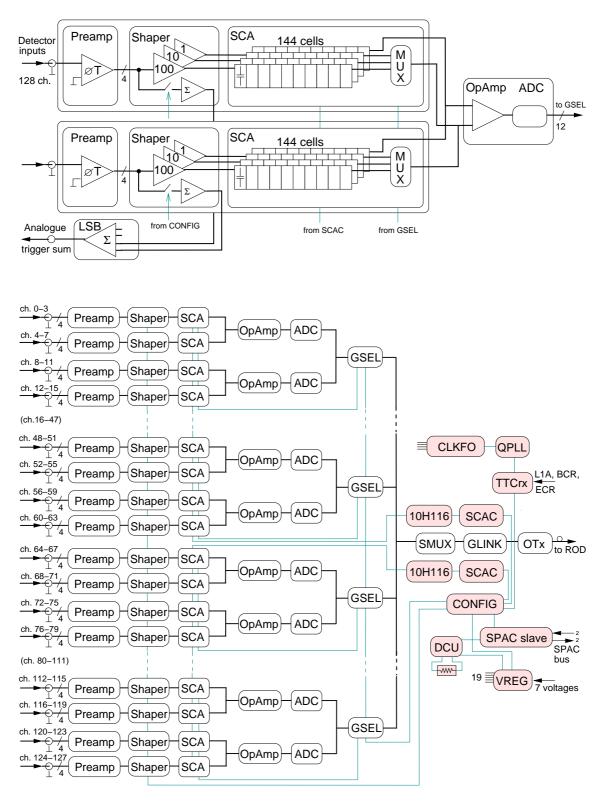

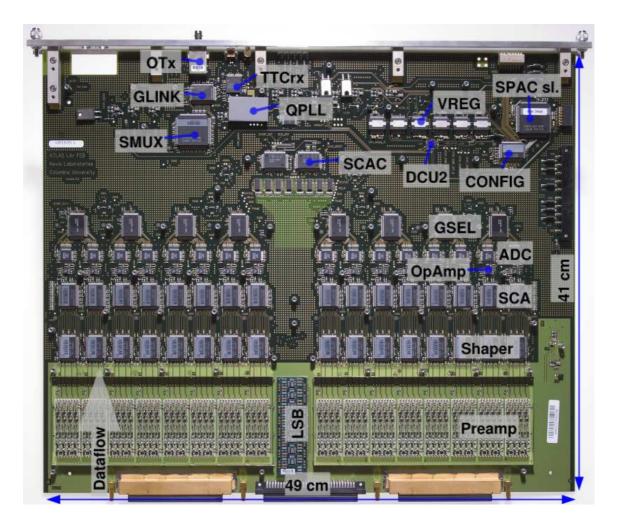

### 3. Overview of the FEB architecture

Block diagrams indicating the main features of the FEB architecture are shown in figure 2, and a summary of the main FEB components is presented in table 3. As the raw calorimeter signals emerge from the cryostat feedthroughs, they are mapped onto the FEB inputs. On the FEB, the signals are first subject to several stages of analog processing. Preamplifier hybrids amplify the raw signals. To reduce the dynamic range requirements of the sampling and digitization stages, the preamp outputs are split and further amplified by shaper chips to produce three overlapping linear gain scales which are each subject to fast analog shaping. The shaped signals are then sampled at the LHC bunch crossing frequency of 40 MHz by switched-capacitor array (SCA) analog pipeline chips, which store the signals in analog form during the L1 trigger latency.

For events accepted by the L1 trigger, typically five samples per channel are read out from the SCA using the optimal gain scale, and digitized using a 12-bit ADC. The digitized data are formatted, multiplexed, and then transmitted optically out of the detector to the ROD via a single 1.6 Gbps optical output link per FEB.

The FEB implements the first two stages in the summing tree producing analog sums for the L1 trigger. The shaper chips sum their four input channels. The shaper sum outputs are then summed further on plug-in Layer Sum Boards (LSB) mounted on the FEB. The LSB outputs are sent off of the FEB to trigger boards mounted in the same crate, which perform further summing and processing.

For configuration and operation, the FEBs require a number of external control signals. The 40 MHz LHC clock, as well as the L1 trigger signal and a few other signals synchronous with the clock, are delivered via the ATLAS Trigger and Timing Control (TTC) system [10]. The FEB is configured and monitored via a dedicated "Serial Protocol for ATLAS Calorimeters (SPAC)" [11] serial control link, operating at 10 MHz.

The following sections describe each of the blocks on the FEB architecture in more detail.

**Figure 2.** FEB block diagrams, with the upper figure showing more details of the analog processing for a block of eight channels, and lower one showing the architecture of the entire 128-channel FEB.

| T  | <b>Table 3.</b> The acronyms of the main active components of the FEB, the number per 128-channel FEB, and the |  |  |  |  |  |  |  |  |

|----|----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| c  | component's functionality. The components are grouped according to the semiconductor technology used in        |  |  |  |  |  |  |  |  |

| tl | their production. The last column lists the section of this paper where more details can be found.             |  |  |  |  |  |  |  |  |

| ĺ  | Production         Component         Number         Brief Description         Section for                      |  |  |  |  |  |  |  |  |

| Production | Component  | Number  | Brief Description                    | Section for |

|------------|------------|---------|--------------------------------------|-------------|

| Process    | Name       | per FEB | of Functionality                     | Details     |

| Hybrid     | Preamp     | 32      | First stage amplification            | 4.1         |

|            | Preshaper  | 32      | Amplification, preshaping for HEC    | 4.2         |

| AMS BiCMOS | Shaper     | 32      | Amplification and shaping            | 4.3         |

| DMILL      | SCA        | 32      | Sampling and analog pipeline         | 4.4         |

|            | SMUX       | 1       | 32:16 multiplexor                    | 7           |

|            | TTCrx      | 1       | Trigger and timing control receiver  | 10.1        |

|            | SPAC slave | 1       | Serial control interface             | 10.3        |

|            | CONFIG     | 1       | Configuration controller             | 10.3        |

| DSM        | GSEL       | 8       | Gain selection, data formatting      | 4.5         |

|            | SCAC       | 2       | SCA controller                       | 5           |

|            | CLKFO      | 7       | Clock fanout                         | 10.2        |

|            | QPLL       | 1       | Quartz-crystal phase-locked loop     | 10.2        |

|            | DCU        | 2       | Temperature and voltage monitor      | 11          |

| COTS       | OpAmp      | 32      | Match SCA output to ADC input        | 4.5         |

|            | ADC        | 16      | 12-bit digitization                  | 4.5         |

|            | 10H116     | 8       | SCA address bus driver               | 6           |

|            | GLINK      | 1       | 1.6 Gbps Serializer                  | 7           |

|            | OTx        | 1       | VCSEL-based optical transmitter      | 7           |

| STm RHBip1 | VREG       | 19      | Radiation-tolerant voltage regulator | 11          |

# 4. Analog Signal Processing

As depicted in figure 2, and described in more detail in the following, the analog processing performed by the FEB includes amplification, shaping, storage in an analog pipeline, and then digitization for events accepted by the L1 trigger.

# 4.1 Preamplifiers

For the ATLAS EM calorimeters (both barrel and endcaps), the raw calorimeter signals are cabled out of the detector and received on the FEBs. Preamps mounted on the FEB provide the first step of analog processing. A similar situation applies to the FCAL signals.

The raw calorimeter signal is an approximately triangular current pulse having a risetime of a few ns and a falling edge extending for the total drift time ( $\approx 400$  ns) of electrons in the LAr gaps. The response of the EM calorimeters to an electron results in a current of typically  $\approx 2-3 \,\mu$ A/GeV. The dynamic range of interest corresponds, therefore, to currents in the range of nA up to several mA.

The LAr preamps [12] are coupled to the detector by a transmission line. As the signal duration is long compared to the shaping time, current preamps are used which provide a voltage output

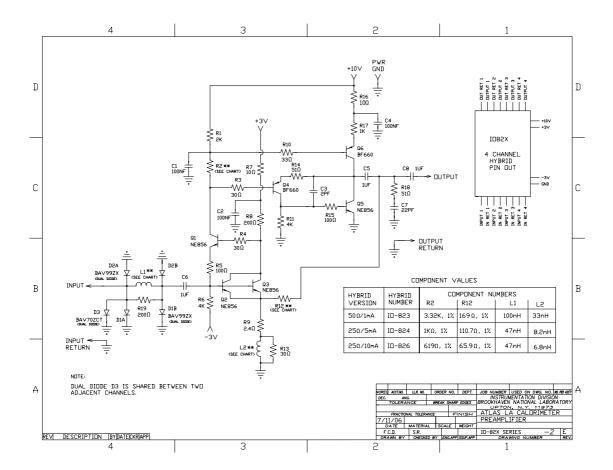

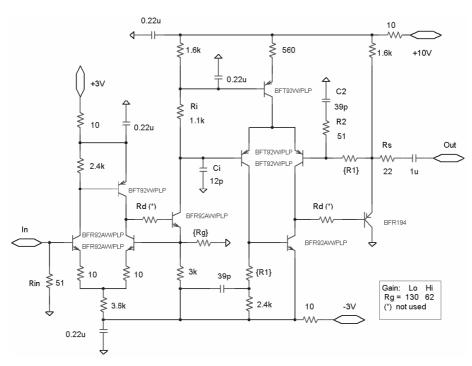

Figure 3. Schematic of one channel of the four-channel preamplifier hybrid.

directly proportional to the input current. The principle of coupling a preamp to a high capacitance detector is described in Reference [13].

The preamp circuit schematic is shown in figure 3. The main characteristic of the ATLAS preamp is the use of a local feedback in the input stage to attribute the functions of low noise and high dynamic range to two different transistors. This circuit configuration allows excellent linearity and noise performance, with relatively low power ( $\approx 50$  mW per channel). The gain (i.e. the transresistance) and the input impedance can be chosen independently without changing the power supply voltages and power dissipation.

In order to optimize the match of the preamp characteristics to the calorimeter cell to which it is connected, three different variations, or "flavors", of preamp are used. As summarized in table 4, the flavors differ in terms of their input impedance, gain (ie. transimpedance), and dynamic range. These variations are achieved by using the appropriate values of components R2, R12, L1, and L2 in the schematic of figure 3. Flavor 1 is used in the presampler and in the front sections of the EM calorimeter, Flavor 2 is used for the FCAL as well as the EM middle/back sections for lower  $|\eta|$ , and Flavor 3 is used for the EM middle/back sections for higher  $|\eta|$ .

The preamp is realized as a four-channel thick-film hybrid, measuring 55 mm  $\times$  23 mm. The hybrid is equipped with gold-plated pins that plug into matching sockets mounted on the FEB

| Preamp | Input Impedance | Transimpedance | Maximum Input | Typical Detector |

|--------|-----------------|----------------|---------------|------------------|

| Flavor | $(\Omega)$      | $(\Omega)$     | Current (mA)  | Capacitance (pF) |

| 1      | 50              | 3k             | 1             | 160 - 500        |

| 2      | 25              | 1k             | 5             | 300 - 2000       |

| 3      | 25              | 500            | 10            | 400 - 2000       |

Table 4. Characteristics of the three different flavors of preamps.

PCB, allowing customization of the FEBs for the different calorimeter sections by insertion of the appropriate preamp hybrids.

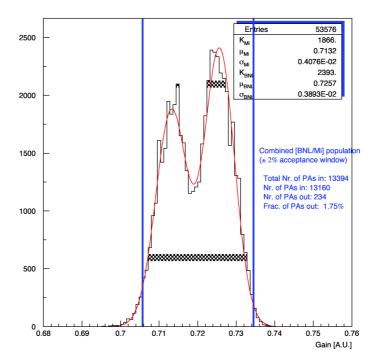

Production of the preamps was split approximately equally between Brookhaven National Lab (BNL) and INFN Milano. Each site procured all components for their local production, and some differences resulted. Measurements performed during the pre-testing of the hybrids revealed slightly different performance parameters [14]. The most significant difference was in the gains. For example, figure 4 shows the measured gains for the 25  $\Omega$  5 mA version of the preamp, for which two different distributions are clearly visible. The lower gaussian corresponds to the INFN preamps, with a mean gain which is 1.7% below that of the BNL preamps. Each distribution separately has a Gaussian width of  $\sigma \approx 0.5\%$ . Within each lab, an acceptance window of  $\pm 2\%$  was applied during preamp testing. For the precision readout, each channel is separately calibrated and therefore matching of the absolute gain is not relevant. However, to ensure sufficiently uniformity for the L1 trigger sums, the gains are required to be uniform within < 5%. As shown in the figure, less than 2% of the hybrids would fall outside a  $\pm 2\%$  acceptance window applied to the combined distribution, and all are well within the L1 specification. The slight differences, therefore, are not considered an issue.

#### 4.2 Hadronic Endcap Preshapers

For the Hadronic Endcap (HEC) calorimeters, cryogenic preamps are mounted directly on the detector in the liquid argon. The HEC cryogenic electronics system is described in Reference [15]. The preamp outputs are driven on cables out of the cryostat to the FEBs.

Instead of the plug-in preamp hybrids used for the rest of the LAr subsystems, the HEC FEBs are equipped with plug-in "HEC preshapers" [16] that are designed to be pin-to-pin compatible with the preamp. A schematic of the HEC preshaper is shown in figure 5. The HEC preshapers include a pole-zero cancellation to adapt to the widely varying HEC detector capacitance. In addition, the HEC preshaper invert, amplify and pre-shape the signals so that they output to the FEB shapers signal that have the same polarity and approximately the same shape as for the rest of the LAr calorimeters. With these adaptations, the same FEBs are used for all LAr calorimeters.

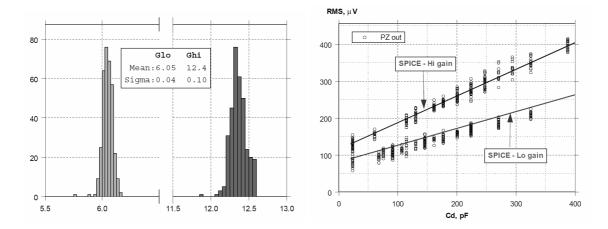

To optimize the match of the preshaper to the HEC channel to which it is connected, 14 different preshaper pole-zero time constants are needed. In fact, since the preshapers are mounted on both sides of the FEB, a total of 28 different preshaper versions is required. Depending on the value of component  $R_G$ , the preshaper has a nominal gain of either 6 ("LO") or 12 ("HI"). Figure 6 shows the measured gains for 168 hybrids, which are in good agreement with the design values. The dispersion among hybrids has an RMS of less than 1.5%, satisfying the uniformity requirement

Figure 4. Distribution of gains measured for the 25  $\Omega$  5 mA version of the preamplifier hybrids. For more details, see the text.

Figure 5. Schematic of one channel of the four-channel HEC preshaper hybrid.

set by the L1 trigger. Figure 6 also shows the measured noise as a function of detector capacitance, with the results of Spice simulations superimposed on the measurements; good agreement is seen between the noise levels achieved and those expected by simulation.

**Figure 6.** Results of measurements of a sample of 168 HEC preshapers. The left plot shows the measured gains, while the right plot shows the measured and simulated noise levels as a function of detector capacitance.

#### 4.3 Shaper

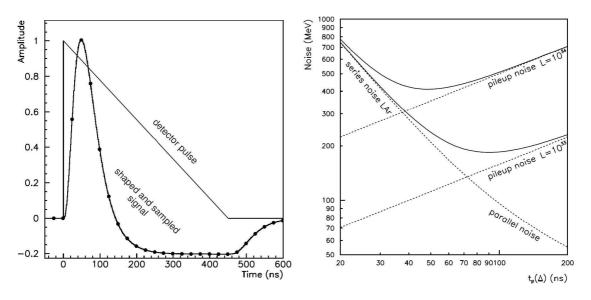

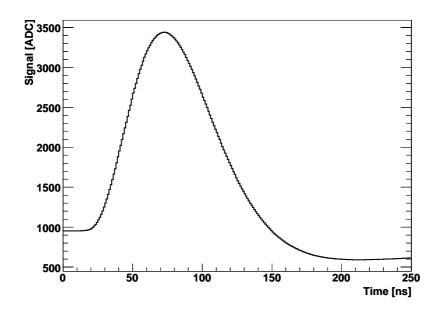

The preamp/preshaper outputs are AC-coupled into a four-channel shaper chip [17], which applies an CR-(RC)<sup>2</sup> analog filter to the signals in order to optimize the signal-to-noise ratio. The differentiation serves to remove the long tail from the detector response, while the two integrations limit the bandwidth in order to reduce the noise. The CR-(RC)<sup>2</sup> filter architecture, with transfer function  $H(s) = (\tau s)/(1 + \tau s)^3$ , is a good compromise between the number of stages (and corresponding power consumption) and the performance, since it is only 10% worse than an ideal filter.

The RC time constant of the shaping function is set to 13 ns, representing a compromise between minimizing pile-up noise, which increases for slower shaping, and thermal noise, which decreases for slower shaping. The characteristic form of the resultant output signal shape is shown in figure 7(a). For the typical detector capacitance, the peaking time of the signal when convoluted with a 450 ns triangular input current is  $\approx 35$ -40 ns. Figure 7(b) demonstrates that this value of peaking time is close to optimal for the LHC design luminosity of  $10^{34}$  cm<sup>-2</sup> s<sup>-1</sup>. For lower luminosities, further downstream digital filtering can be used to achieve an effectively longer shaping time, and subsequently better noise performance. Another consideration is that the shaped signals are sampled at the 25 ns LHC bunch-crossing rate, so even faster shaping would start to suffer from aliasing effects.

In addition to shaping, the shaper provides additional amplification, so that the preamp noise will dominate over the contributions from later stages. To achieve the full dynamic range, the shaper splits each signal to provide three overlapping linear gain scales, with gain ratios of  $\approx 10$ . The absolute gains are 0.8 (LO gain), 8.4 (MED gain) and 82 (HI gain). The shaper also includes one "Dummy" output which has no input signal but the same output stage as the analog signals. The Dummy channel thereby provides a measurement of the on-chip noise. As described in section 4.4, this signal is connected to the input Reference channels of the SCA analog pipeline in order to provide a "pseudo-differential" architecture, with the goal of reducing low frequency noise.

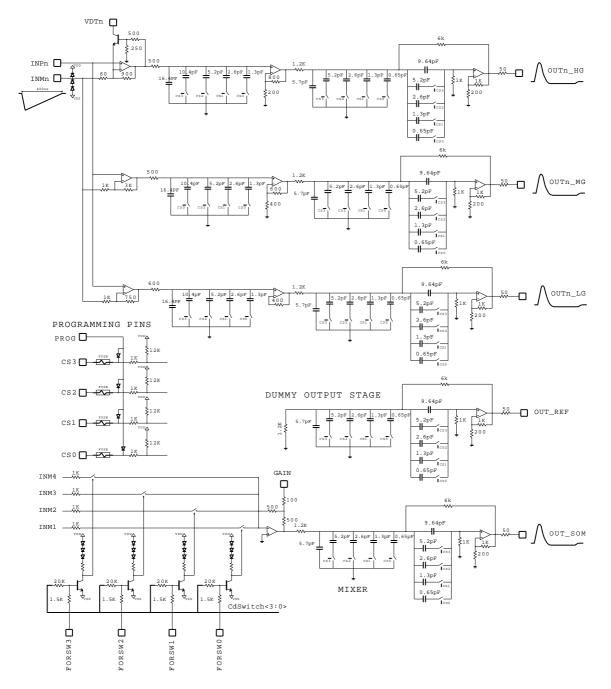

The shaper chip also incorporates a "Linear Mixer" (LM) stage, represented by the  $\Sigma$  symbol in figure 2, which provides an additional output corresponding to a shaped sum of the four input

**Figure 7.** (a) Shape of the signal output from the shaper chip. The dots indicate the position of samples separated by 25 ns. (b) Total noise versus shaping time for luminosities of  $10^{33}$  and  $10^{34}$  cm<sup>-2</sup>s<sup>-1</sup>. Also shown are the separate contributions from pile-up noise and from electronics (series and parallel) noise.

channels. The channels are summed before shaping, and then the sum is subject to a CR-RC filter before being output. Depending on how the "Gain" pin on the shaper package is connected on the FEB PCB, the LM gain can be set to either one or three. As described in more detail in section 9, the LM output signals are used in the generation of analog sums for use by the L1 trigger system. Programmable switches are used to enable or disable individual channels in the trigger sum, allowing the disabling of noisy or faulty channels. The values of the switches are set, and can be read back for verification, via the SPAC slow control link to the FEB.

The architecture of the shaper chip is depicted in figure 8. As shown, the CS0 through CS3 inputs are connected to fuses which can be blown to connect additional capacitors in the shaping stages. Their purpose is to allow tuning of the RC time constant in the presence of unavoidable process variations in the values of the on-chip resistors and capacitors.

The shaper is realized as a four-channel ASIC implemented in the AMS 1.2  $\mu$ m BiCMOS technology [18], and is packaged in a 100-pin rectangular QFP package with 0.65 mm pitch. Some of the relevant shaper parameters and performance figures are summarized in table 5.

### 4.4 SCA analog pipeline

The shaper output signals are sampled at 40 MHz and stored in analog form by a switched-capacitor array (SCA) analog pipeline. The SCA stores the analog signals during the L1 trigger latency in pipelines of 144 cells, and further serves as a multiplexor and de-randomizing buffer in front of the ADC for triggered events. The SCA is designed to allow simultaneous Write and Read operations. Separate 8-bit Write addresses (WADD) and Read addresses (RADD), as well as a 40 MHz Write clock (WCLK) and 5 MHz Read clock (RCLK) must be provided from off-chip to control the operation of the SCA.

Each SCA chip processes all three gain scales for each of four calorimeter channels. In addition, an extra so-called "Reference" channel is associated with each group of three gains corre-

**Figure 8.** Block diagram of the shaper architecture. One of the four identical signal channels is shown in the upper half of the figure, while the fuse programming pins, Dummy output and Linear Mixer circuits are shown in the lower half.

sponding to a calorimeter channel, so the SCA chip contains a total of 16 analog pipeline channels. On the FEB PCB, the inputs of the four Reference channels are connected together to the "Dummy" output of the shaper. The Reference channel is treated by the SCA exactly as the other channels and its output is subtracted from the signal output during the Read operation. This subtraction is performed off-chip. This pseudo-differential operation is employed to reject the major part of

| Parai      | neter      | Value                       |  |  |

|------------|------------|-----------------------------|--|--|

| Number o   | f channels | 4                           |  |  |

| Die        | size       | $4 \times 4.5 \text{ mm}^2$ |  |  |

| Voltages   | VDD        | 4.5 V                       |  |  |

|            | VSS        | -3.0 V                      |  |  |

| Power con  | nsumption  | 500 mW total                |  |  |

| Output sig | gnal swing | -2 V to +3.5 V              |  |  |

| Input im   | pedance    | $50\Omega\pm15\%$           |  |  |

| Gain       | HI         | 82                          |  |  |

|            | MED        | 8.4                         |  |  |

|            | LO         | 0.8                         |  |  |

| Noise      | HI         | 850                         |  |  |

| (µV)       | MED        | 400                         |  |  |

|            | LO         | 250                         |  |  |

| Line       | arity      | $\pm 0.2\%$                 |  |  |

| Cros       | stalk      | < 0.1%                      |  |  |

**Table 5.** Some of the parameters and performance measures for the shaper ASIC.

the coherent noise generated before and inside the chip such as clock feedthrough and couplings through the substrate. It also improves the power supply rejection ratio (PSRR) of the SCA chip.

The output of the shaper is DC-coupled to the input of the SCA. As a result, the SCA is asymmetrically powered (VSS=-1.7 V, VDD=+3.3 V) to deal with input signals in the range from -0.9 V to +2.5 V with a baseline voltage of 0 V.

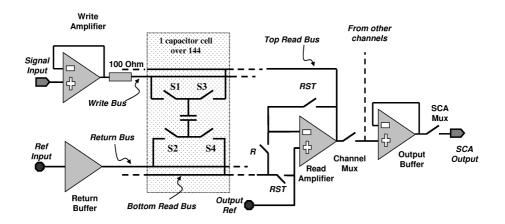

More details about the SCA design can be found in Reference [19]; here we describe the main design features and characteristics. A depiction of the structure of one channel of the SCA is shown in figure 9. Each pipeline contains 144 identical cells. Each cell comprises  $a \approx 1 \text{ pF}$  storage capacitor, and separate switches for Writing (switches S1 and S2 in figure 9) and Reading (switches S3 and S4). Switches S1 and S3, which have to deal with the input signal dynamic range, are CMOS switches, whereas S2 and S4 are simple NMOS switches as they are connected to a fixed intermediate level.

The input signal is connected to the Write bus through a Write amplifier, the aims of which are to limit the voltage swing of the input signal, to present a constantly low capacitive load to the shaper output, and to decrease drastically the level of crosstalk by buffering the flow of signal currents on and off of the SCA chip. The Write amplifier is an operational amplifier connected as a voltage follower. To ensure stable operation, a 100  $\Omega$  p+ diffusion resistor is placed in series between the amplifier output and the Write top bus.

Similarly, a return buffer, connected to the return bus, reduces cross-talk by limiting currents from the common reference pin of the chip. This buffer does not have a wide dynamic range requirement, and so a simple NMOS source-follower is used for this purpose. The common input reference voltage of these 16 followers is generated by a servo-control system which connects the Write return bus to a reference voltage, denoted by VREF.

Figure 9. Block diagram of the SCA analog pipeline design.

During a Write operation, S1 and S2 are closed and the voltage across the capacitor tracks the difference of voltage between the Write bus and the return bus. The effective capacitor charging time constant is  $\approx 2$  ns, set by the value of the capacitance and the ON resistance of the switches. The input signal voltage is sampled and stored on the capacitor at the moment the Write switches are opened again. The timing of the Write switches is designed such that the NMOS transistors of S1 and S2 open with a delay of about 2 ns compared the PMOS transistor in S1. Thus, the opening of switch S2 defines the time of the Write operation. Since S2 is connected to a quasi-invariant voltage (the return bus), both the time of the sampling and the charge injected into the capacitor during the operation are kept independent of the signal value, thus minimizing jitter and avoiding undesirable non-linearity. The typical delay between the rising edge of the differential low voltage input WCLK and the sampling time is 4 ns.

For a Read operation, the corresponding sampling capacitor is put in the feedback of the Read amplifier by closing S3 and S4 after the Read bottom bus has been reset. To reduce the sensitivity to noise injected in the substrate, the top plate of the storage capacitor is the one connected to the sensitive input node of the Read amplifier during the Read operation whereas the bottom plate, which presents a parasitic capacitance to back silicon, is the one connected to the output of this amplifier. As the Write and Read operations are both performed in voltage mode, the gain of the SCA is very close to unity and is, to first order, independent of the value of the storage capacitance.

The Read amplifier has the same open-loop structure as the Write amplifier but uses a PMOS transistor input pair to provide lower white and 1/f noise. Before reading a storage cell, the residual charge stored on the parasitic capacitance of the bottom Read bus needs to be cleared to avoid the mixing of two consecutive signals. During this Reset phase, the RST switches are closed, setting the Read amplifier in voltage-follower mode and discharging the bottom Read bus, while Read switch R is opened, insulating the Read amplifier input from the bottom Read bus capacitance to avoid oscillations. This phase lasts at least 100 ns to allow discharging of the bottom Read bus with sufficient precision. At the end of the Reset phase, the RST switches are opened just before switch R is closed.

At the output of the Read amplifiers, the 12 signal channel outputs are multiplexed by CMOS switches towards the signal output buffer. In the same way, the four Reference channels are mul-

tiplexed towards the Reference output buffer. The commands of the switches are generated by a sequencer within the digital Read logic section. When no channel is selected, the inputs of the two output buffers are clamped by PMOS transistors to VREF.

The output buffers have the same structure as the Write amplifiers (NMOS input), and are designed to be able to drive up to 30 pF for the 5 MHz read-out frequency. To allow multiplexing of two SCA chips to the same external ADC, the output buffers are insulated from the output pads by CMOS switches. The ON resistance of these switches is 400  $\Omega$  and varies by about  $\pm$  15% along the SCA voltage dynamic range. Achieving a good linearity requires that the electronics connected to the SCA outputs have a high input resistance, at least 100 k $\Omega$ . As described in section 4.5, commercial op-amps configured as voltage followers are used for this purpose. Moreover, the outputs of the SCA are never left in a high-impedance state; one of the paired SCA chips is configured to always drive the output lines except for when the other SCA is being read out.

The Read control signals include the 5 MHz Read clock (RCLK) and a Read signal which is used to trigger a Read operation. The 8-bit RADD is transmitted bit-serially to the SCA at the 5 MHz RCLK frequency in order to reduce the number of lines, and associated noise, on the SCA control bus. The SCA internally generates a complete Read cycle which includes cycling the MUX output through each of the four calorimeter channels. For each channel, the gain scale indicated by the two Gain Selection bits (supplied by the Gain Selector chip, as described later) is output.

As described later in section 6, all control signals are transmitted to the SCA chips via a control bus using low voltage, differential signals. These signals are received on the SCA chip and then converted internally to differential CMOS signals for driving the on-chip digital logic.

The SCA chip is realized in the DMILL process, and contains  $\approx 45000$  transistors and 2384 capacitors on a die measuring 4.5 mm  $\times$  4.4 mm. The SCA chip is packaged in the same 100-pin QFP package used for the shaper. For the SCA, two different packaging geometries were used, one with the die mounted up and the other with the die mounted upside down. This was achieved by bending the pins on the chip frame in the appropriate direction before the plastic encapsulation stage. Using this method, half of the chips were packaged in the "standard" geometry and the other half using the "mirror" geometry. The purpose was to allow SCA chips mounted on opposite sides of the FEB PCB to directly share the vias providing the large number of connections to the addresses and control signal buses, as well as power and grounds. This greatly simplified the routing of the FEB PCB. Table 6 summarizes some of the parameters and performance figures for the SCA chip.

# 4.5 Digitization and Gain Selection

As was shown schematically in figure 2, op-amps are used to couple the SCA outputs to the ADC. In particular, two commercial dual op-amp chips (AD8042 from Analog Devices [20]) are used to connect to the commercial 12-bit ADC (AD9042 from Analog Devices [21]), which is operated continuously at 5 MHz. The first pair of op-amps are connected as emitter followers to provide high impedance loads to the two pseudo-differential CMOS SCA output drivers. The second pair perform the differential subtraction in front of the single-ended ADC. In addition, they are operated with less than unity gain to map the SCA output voltage range onto the more limited (1 V) ADC input signal range. Finally, a voltage offset is added such that the pedestal value corresponds to

| Parameters                                  | Value                    |

|---------------------------------------------|--------------------------|

| Power Consumption                           | $290 \text{ mW} \pm 5\%$ |

| VSS, VDD                                    | -1.7 V, +3.3 V           |

| Input Bandwidth                             | 50 MHz                   |

| Input Slew Rate                             | 175 V/µs                 |

| Sampling time jitter                        | $\approx 10 \text{ ps}$  |

| Cell-to-cell sampling time variation        | 1.9 ps/cell              |

| DC Gain                                     | 0.995                    |

| Input range with $< 0.2\%$ integral nonlin. | -0.8 V to 2.9 V          |

| Noise                                       | 290 µV                   |

| Dynamic Range                               | 13.2 bits                |

| Fixed Pattern Noise                         | 250 µV                   |

| Channel Offset Dispersion                   | 12 mV RMS                |

| Droop rate                                  | < 0.54 V/s               |

| Crosstalk                                   | < 0.01%                  |

Table 6. Some parameters and performance measures for the SCA chip.

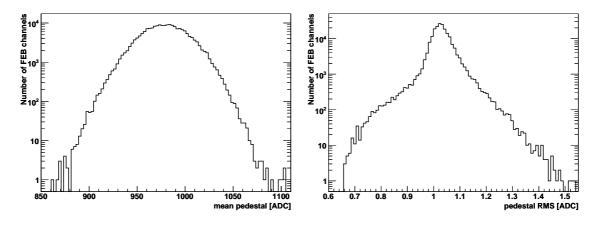

$\approx$  1000 ADC counts, allowing measurements on both the positive and negative lobes of the shaped calorimeter signals.

The 12 single-ended TTL digital outputs of the ADC are interfaced to a Gain Selector (GSEL) ASIC [22]. To reduce the event size and required readout bandwidth, typically only one of the gain scales is read out for each channel. For optimal precision, one would like to read out the scale which has the highest gain and yet is not saturated. The gain selection needs to be performed individually for each calorimeter channel, and separately for each Level 1 trigger. The GSEL is designed to perform this gain selection, and can be configured for calibration purposes to read out either one, two, or even all three gain scales. During normal physics running, the GSEL is configured to operate in "Auto Gain" mode, where the gain scale is selected dynamically for each channel and trigger by first digitizing the peak sample on a specified gain. This value is then compared by the GSEL against two 12-bit thresholds, downloadable for each channel separately, to determine the optimal gain scale to be used. The five samples of the given event are then digitized, all on the selected gain scale. The gain selection method thus requires that six digitizations be performed per channel in order to get the final five samples, but avoids systematic effects which would be encountered in combining the five samples if they were not all digitized on the same gain scale. The GSEL communicates the appropriate gain via two gain selection bits sent to the output multiplexor sections of the corresponding SCA chips.

The GSEL was designed, prototyped and tested first using the DMILL process. However, when the SCA Controller (see section 5) was developed in the DSM process, the opportunity was taken to target the GSEL design also to DSM, using essentially the same Verilog design as for the DMILL GSEL version. The minimum DSM production run was such that the SCAC, GSEL and also CLKFO chips were all produced on the same wafers with essentially no extra cost, apart from packaging, than would have been incurred to produce only the SCA Controller chips.

The DSM GSEL is realized as a 4 mm  $\times$  4 mm ASIC implemented in the radiation-tolerant DSM process, and was packaged in the same 100-pin QFP package as the shaper and SCA. One GSEL ASIC handles the outputs of two ADCs, corresponding to 16 channels. The GSEL design incorporates features to protect against SEU-triggered corruption of the downloaded parameters needed to configure and operate the GSEL. Hamming code bits are used to provide Error-Detection-and-Correction (EDC) functionality such that, if any single bit gets flipped, the error is detected and automatically corrected. An error flag is set in the output data in order to allow monitoring of the rate of single-bit errors. If two bits gets flipped, the error can be detected but not corrected, so an error flag is set to indicate the need to download the parameters again via SPAC in order to fix the problem.

# 5. SCA Controller and FEB Digital Control

The SCA Controller (SCAC) ASIC [23, 24] provides the main digital control of the FEB. The SCAC receives the CLK and trigger information, and generates the WADD and RADD sequences for the SCA pipelines. In addition, the SCAC controls the flow of the SCA readout through its communication with the GSEL.

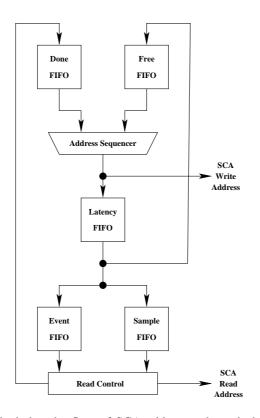

The main SCAC functionality, namely the SCA WADD and RADD bookkeeping, involves cycling the 144 pipeline addresses of the SCA through a system of FIFOs. The SCA addresses are gray encoded, to reduce address pattern noise on the FEB and inside the SCA. To achieve this noise reduction, the addresses must be maintained in sequential order as much as possible. As illustrated in figure 10, the movement of SCA addresses takes the following path:

- After a SCA cell number is used for the SCA WADD for a particular bunch crossing, it is written into the Latency FIFO, which stores the sequence of SCA cells corresponding to the bunch crossings of the L1 trigger latency. The cell numbers are stepped through the Latency FIFO every 25 ns. The depth of the FIFO is programmed, depending on the actual value of the L1 latency, such that a given cell number emerges from the FIFO at the time that the L1 trigger decision for the relevant bunch crossing arrives at the FEB.

- Cells which emerge from the Latency FIFO and are not part of an L1 trigger are transferred to the Free FIFO, which contains addresses which are available for use as WADD in upcoming bunch crossings.

- 3. Those addresses emerging from the Latency FIFO which are part of a L1 triggered event are transferred to the de-randomizing buffer of samples awaiting digitization. The SCAC will typically be configured to read out five consecutive samples for each triggered event. The relevant cell addresses are stored in either the Event FIFO or the Sample FIFO. The Event FIFO stores some event status information and the cell address of the peak sample of the event. The Sample FIFO stores the remaining non-peak sample addresses.

- 4. After the signal samples corresponding to a particular cell address have been fully digitized, the address is again available for re-use. However, in order to keep the gray encoded addresses as sequential as possible, these cells are not immediately put into the Free FIFO. Instead, they are transferred to the Done FIFO.

**Figure 10.** Block diagram depicting the flow of SCA addresses through the various FIFOs of the SCA Controller.

5. Every 25 ns, the Address Sequencer compares the addresses at the top of the Free FIFO and Done FIFO and chooses the one which most closely preserves the ongoing sequence of WADD. In this manner, the addresses in the Done FIFO, corresponding to samples read from previous L1 triggers, will be inserted back into the correct sequence.

The number of events that can be stored in the de-randomizing buffer of the SCA depends on the L1 latency and on the number of samples to digitize per L1 trigger. The 144-capacitor depth of the SCA was chosen to provide at least an eight-event buffer, assuming a maximum L1 latency of 2.5  $\mu$ s (100 bunch crossings) and five signal samples per event. The deadtime caused by the FEB is then less than a few percent for the maximum allowed L1 trigger rate of 75 kHz. The FE readout system does not send a "Busy" signal to the trigger system. Instead, the L1 central trigger processor models the status of the SCAC and implements a leaky bucket algorithm to avoid issuing additional triggers when the SCA buffers are full.

Via the SPAC system, the L1 latency is configurable in the SCAC between 64 and 127 bunch crossings. In addition, the SCAC can be configured to read from 1 to 32 signal samples for each L1 trigger. These signal samples can form an arbitrary pattern (with gaps) of up to 32 bunch crossings in length. One sample is designated as the peak sample and is read first to perform the gain selection. The remaining signal samples are read in sequence.

From the TTCrx chip [10] located on each FEB, the SCAC receives the 40 MHz clock as well as the L1 Accept (L1A) signal, Reset signals for its internal Bunch Crossing and Event Number counters, and a signal for initialization. The bunch counter number (BCID) is used in ATLAS

to align the various detector readout elements in order to correctly combine them when building an event. More details on the trigger and timing control are provided in section 10.1. In order to synchronize the readout operation, the SCAC provides the GSEL with the RADD as well as other information (such as BCID as well as SCAC internal status bits) required for the readout data stream.

The SCAC functionality was first implemented using the radiation-hard DMILL technology. However, the DMILL design resulted in a rather large die size and limited operating speed margin. It was decided, therefore, to perform a new SCAC design using the DSM technology. The increased speed and density of the DSM process allowed inclusion in the design of a number of features aimed at mitigating SEU effectsm including Hamming code bits as well as using triple-redundant flipflops and majority voting. More details about the SEU hardening will be presented in a subsequent publication about the radiation performance of the entire ATLAS LAr FE readout.

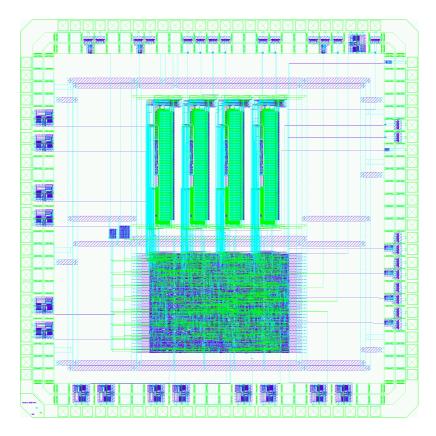

The DSM SCAC is packaged in the same 100-pin QFP package as the shaper, SCA and GSEL. The minimum size of the DSM SCAC die was  $2.7 \text{ mm} \times 2.7 \text{ mm}$ . Due to quantization requirements on the reticle, the edges of the die were required to be a multiple of 2 mm. While the design could have fit into a 2 mm  $\times$  4 mm area, it was decided to keep the geometry square to simplify packaging. The final die size was therefore 4 mm  $\times$  4 mm. A drawing of the layout can be seen in figure 11. The layout is pad-limited, with the core occupying less than one-half of the available space. In addition to the SRAM, the SCAC contains 957 D-flip-flops, including those embedded inside the SRAM blocks. With few exceptions, all I/O to and from the SCAC uses low-voltage differential signal (LVDS) levels, with differential receivers on all input pairs and current mode LVDS drivers on the output pairs.

The SCAC chips were subjected to extensive functional testing before being assembled on to FEBs. The maximum frequency for which the SCAC operated properly ranged from 54.5 MHz to 63.5 MHz, with a mean value of 59.0 MHz and an RMS of 1.1 MHz. These values provide a wide safety margin, given the required operating frequency of 40 MHz.

# 6. SCA control and Address Bus

Each of the two SCAC chips on one FEB controls a total of 16 SCA chips, corresponding to 64 readout channels. For proper operation, the SCAC must send to the 16 SCA chips the associated WADD, RADD and control lines. Given the number of SCA chips and control signals required, the SCA control was implemented as a bus, with one driver per line driving all 16 SCA chips.

The SCA control bus is driven differentially using commercial MC10H116D chips [25]. The 10H116 chips are powered with voltage rails of +3.3 V and -1.7 V in order to match those of the SCA chips. The SCA control bus lines are routed on an internal layer of the FEB PCB, with grounds on neighboring layers (see section 12). The bus is terminated at both ends with 27  $\Omega$  resistors, with the far end termination connected to VSS through a 470 pF center-tap capacitor. Simulations including the distributed SCA loads showed that the resultant signals are very clean, with fast rise and fall times and little overshoot, and an amplitude of  $\approx$  400 mV. These expectations were confirmed by measurements. The delay between the signals at the first pair of SCA chips on the bus and at the last (eighth) pair is measured to be  $\approx$  2 ns, in agreement with simulation. This effect implies a channel dependence of the signal sampling time that, if uncorrected, would

**Figure 11.** Diagram showing the layout of the DSM SCA Controller ASIC. The four double-width SRAM blocks used to implement the SCA address FIFOs are visible in the upper region of the core, while the combinatorial and sequential logic occupies the lower region of the core.

correspond to a Gaussian sigma of  $\approx$  580 ps. However, since the effect is perfectly systematic and predictable, it can easily be corrected.

As described in section 4.4, pairs of SCA chips mounted on opposite sides of the PCB were packaged such that they could share vias for the control lines. This greatly reduced the routing complexity, and also reduced loading of the bus due to vias.

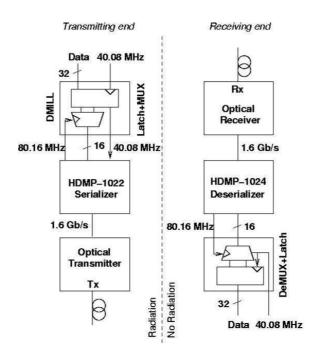

# 7. Output optical link

The formatted event fragments of 16-bit words from each GSEL are serialized in a sequence of steps that results in a single 1.6 Gbps bit-serial output stream, transmitted via optical link from each FEB. The basic architecture of the optical link is shown in figure 12.

The first step in the serialization is performed by the GSEL. For each of its two event fragments of 16-bit words, the GSEL outputs two bits parallel at 40 MHz, taking eight 40 MHz clock cycles to output each partially serialized 16-bit word. The bits are transmitted from the GSEL chips over LVDS-like signal lines.

With eight GSEL chips per FEB, and with each GSEL outputting four data lines (two event fragments, each with two data lines), the SMUX chip [26] receives a total of 32 data bits at 40 MHz. The SMUX then performs a 2:1 multiplexing and a level shifting from LVDS to TTL in order to

**Figure 12.** Architecture of the transmission end (left side) and reception end (right) of the 1.6 Gbps FEB output data optical link. The transmitter is mounted on the FEB and the receiver on the ROD.

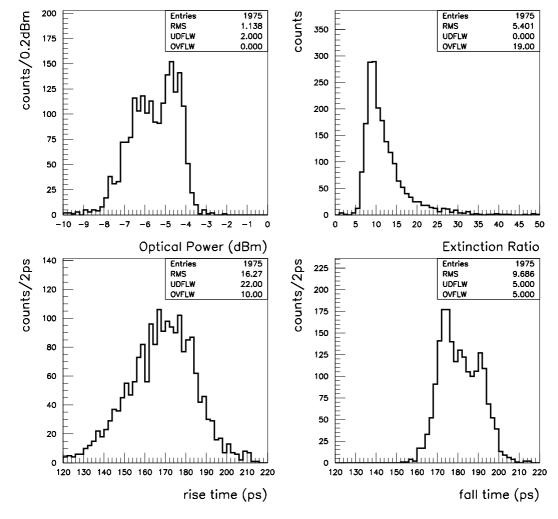

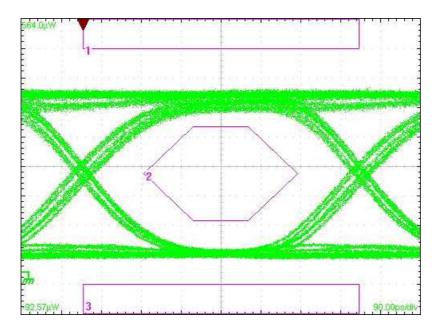

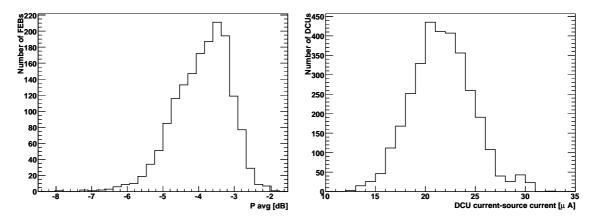

generate an output stream of 16 bits at 80 MHz. In addition, the SMUX generates a FLAG, which is HI (LO) for the MUX cycle when data from channels 0 - 63 (64 - 127) are sent the GLINK. The 16 SMUX data out signals and FLAG are then transmitted at 80 MHz to the commercial "GLINK" serializer chip (HDMP-1022 from Agilent Technologies [27]), which adds protocol and control bits and produces a single serial output stream of 1.6 Gbps. In the final step, this serial stream is converted to an optical signal and transmitted off of the FEB via a custom-built optical transmitter (OTx) module which includes a commercial driver chip (SY88922V from Micrel Inc. [28]) and a 850 nm VCSEL (TTR-1A43 from TrueLight Corp. [29]) for converting the signal from electrical to optical. Table 7 lists the parameters measured, and acceptance windows applied, during QC measurements of the OTx. In addition, an eye mask test, and bit error rate tests at 0 dB and 10 dB attenuated optical power were also carried out. The bit error rates in both cases were required to be less than  $10^{-12}$ . The distributions for several OTx parameters are shown in figure 13, while figure 14 gives a typical eye diagram of the optical signal from the OTx. Detailed information about the QC tests of the OTx can be found in Reference [30].

Multimode 50  $\mu$ m core graded-index (GRIN) fiber is used to carry the signal from the FEB to the ROD. At the ROD end of the fiber, the 1.6 Gbps optical signal is converted back to an electrical signal via a PIN-diode based custom-built optical receiver (ORx) module. It is then de-serialized by the GLINK receiver (HDMP-1024) [27] back into an image of the 16 bits at 80 MHz data stream output from the SMUX.

#### 8. FEB output data format

The GSEL formats the output data for the 8 channels digitized by a single ADC into an event

| Table /. | Parameters | measured, | and the | corresponding | acceptance | windows, | during th | e tests | OI | the | UIX |

|----------|------------|-----------|---------|---------------|------------|----------|-----------|---------|----|-----|-----|

| modules. |            |           |         |               |            |          |           |         |    |     |     |

| Parameter                        | Units | Min. Value | Max. Value |

|----------------------------------|-------|------------|------------|

| Average optical power            | dBm   | -7.5       | -3.5       |

| Extinction ratio                 | -     | 6.0        | -          |

| Rise time                        | ps    | -          | 220        |

| Fall time                        | ps    | -          | 220        |

| Deterministic jitter (peak-peak) | ps    | -          | 125        |

| Random jitter (RMS)              | ps    | -          | 10         |

**Figure 13.** Distributions of optical power, extinction ratio, rise time, and fall time measured during QA tests of the OTx modules.

fragment of 16-bit words according to the format shown in figure 15. The event fragment contains one Frame Start word, two Event Header words, data words carrying the calorimeter signal data, one Event Trailer word, and at least one Frame End word to separate from the next event. For all

**Figure 14.** An eye diagram demonstrating the eye mask test of a typical OTx module. The horizontal scale corresponds to 90 ps/division.

| Frame start tag |        | 1 | 1 | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |

|-----------------|--------|---|---|---------------------------------------|

| Event header    |        | 0 | Р |                                       |

|                 |        | 0 | Р |                                       |

|                 |        | 0 | Р |                                       |

|                 |        | 0 | Р |                                       |

|                 |        | 0 | Р |                                       |

| data            |        | 0 | Р |                                       |

| Sample data     | sample | 0 | Р |                                       |

|                 | per sa | 0 | Р |                                       |

|                 | ă      | 0 | Р |                                       |

|                 |        | 0 | Р |                                       |

|                 |        | 0 | Р |                                       |

| Event trailer   |        | 0 | Р | 0 0 1 S E SCAC status 1               |

| Frame end tag   |        | 0 | 0 | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0       |

**Figure 15.** Readout event format for the ATLAS LAr FEB. See more details in the text. For each word, bit 0 is listed in the rightmost column, proceeding toward bit 15 in the leftmost column.

words except for Frame Start and Frame End, Bit 14 serves as a parity (P) bit, and is set in the GSEL to the appropriate value to ensure odd parity for each 16-bit word.

The first 16-bit word is the Frame Start word, defined as \$FFFF, which signals to the ROD the

start of a new event. The first of two Event Header words follows, and carries the 4-bit ID number of the corresponding ADC and an 8-bit EVENTN field that includes a 5-bit event number and the 3-bit phase of the 5 MHz RCLK with respect to the 40 MHz clock for this L1Accept. The second word contains the 12-bit BCID number for this L1Accept.

The number of signal data words per event fragment depends on the number of samples and number of gains configured to be read out. For each sample, there is first a sample header word, which contains the 8-bit SCA cell number, three "sample mode" bits, and one bit (denoted by A in figure 15) which has a value of 0 for normal data and 1 for data taken in a mode where configurable test data is transmitted instead of data from the ADC. The sample mode bits indicate whether the sample in question is the first (F) or last (L) sample of the event, or whether the so-called "Backporch" (B) bit has been set for this event. If the Backporch bit is set in auto-gain mode, the gain selection algorithm was modified to prevent any channel from using a higher gain than in the previous event. This flag can be set by the SCAC for events that occur less than some specified time (for example, the total LAr drift time of  $\approx 400$  ns) after the previous event, with the goal of preventing an incorrect gain selection for the second event in cases of large signals in the first event.

The sample header word is followed by  $n \times 8$  words containing the ADC data for that sample, where *n* is the number of gains to be read out. Each ADC word includes the 12-bit ADC value plus two bits which encode the gain.

The event trailer word contains the 8-bit SCAC status word, with bits indicating SEU-induced single- and double-bit errors, as well as other SCAC error and status conditions. Bits 9 and 10 of the event trailer word are used as flags to indicate that single- or double-bit errors, respectively, have been detected in the EDC logic of the GSEL.

The final word in the event is the Event End word, defined to be \$0000. Detection of this word indicates to the ROD that the event has ended. Since words of this value are sent by the FEB between events, the ROD simply waits for the next occurrence of \$FFFF to indicate the arrival of a new event.

# 9. Level 1 Trigger Summing

In addition to signals from the muon detectors, the ATLAS L1 trigger system [5] considers the energies deposited in the calorimeters in regions of reduced granularity. These trigger signals are produced via a chain of analog summing, the first two stages of which are performed on the FEB.

The calorimeter signals are proportional to energy, and must be transformed to transverse energy for the L1 trigger. This transformation is accomplished through the choice of several gain factors in the L1 summing chain, including the preamp transimpedance, the LM gain, the gain of the Layer Sum Board (LSB) described below, and gains downstream of the FEB in the Tower Builder and Receiver modules (described in more detail in Reference [4]). The overall gain of the L1 summing chain must be such that a 10 mV pulseheight at the L1 preprocessor input would correspond to 1 GeV of deposited transverse energy. The sums must have a saturation level corresponding to 250 GeV transverse energy. The gain uniformity is required to lie within an allowed variation of  $\pm$  5%.

As discussed in section 4.3, each shaper chip has a Linear Mixer (LM) section that sums its four input channels. On-chip logic, addressable via SPAC, allows the contribution of each

| EMB        | Cell Size                     | Number of cells | Width of | LSB    |

|------------|-------------------------------|-----------------|----------|--------|

| Layer      | $(\Delta\eta	imes\Delta\phi)$ | per TT          | LSB sum  | type   |

| Presampler | 0.1 	imes 0.025               | 16              | 1        | S1x16H |

| Front      | 0.1 	imes 0.0003              | 32              | 8        | S8x2   |

| Middle     | 0.025 	imes 0.025             | 16              | 4        | S4x4   |

| Back       | 0.05 	imes 0.025              | 8               | 2        | S2x8   |

Table 8. Trigger Tower (TT) Structure and Layer Sum Board types for the EMB calorimeter.

individual channel to be switched ON or OFF in this trigger sum. This feature allows masking of noisy or bad channels. In addition, this masking ability provides a very useful debugging feature: any single channel of the calorimeter readout can be examined off-detector with an oscilloscope by enabling only that single channel in the appropriate LM sum, and also disabling all other inputs to that particular trigger sum. This feature can be used, for example, to examine any individual channel for high frequency noise that would not be easily visible through the precision readout due to its 40 MHz sampling rate.

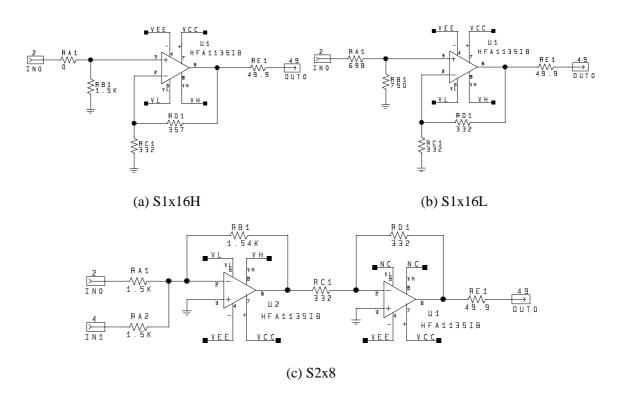

The LM output sums from the 32 shapers per FEB are routed to the inputs of the two Layer Sum Boards (LSBs) [31] which plug into sockets on each FEB. The LSBs use commercial op-amps to provide the next layer in the L1 trigger summing tree. The mapping of EM calorimeter channels onto FEBs has been chosen such that, except in limited regions near the barrel-endcap transition, an individual FEB processes channels from only one longitudinal section (i.e. presampler, front, middle, or back). In the EMB, all Level 1 trigger towers are of size  $\Delta \eta \times \Delta \phi = 0.1 \times 0.1$ , and the analog trigger sums are made using four different types of LSBs, with 1, 2, 4, or 8 inputs (see table 8). The LSB is designated  $n \times m$ , in which n is the number of inputs to each sum and m is the number of summed outputs on the LSB. In the case of the S1x16 LSB, a suffix (L, H, M) is applied to denote the channel gains, as discussed below. In the endcap calorimeters the trigger tower structure is somewhat more complex, but the same types of LSBs are used, employed in different ways.

The LSBs provides sums with a gain of either one or two, depending on the LSB type (with exceptions for FCAL LSBs). The LSBs are required to have a noise which is small compared to the preamp noise, and to provide a voltage clamp at  $\approx 3$  V, with rapid recovery from saturation. The LSBs are non-inverting. There are two basic designs, a single-stage non-inverting configuration (figures 16a and 16b) and a two-stage summing configuration (figure 16c). The former is used only for the S1x16 LSBs, while the latter is used for all other types. The LSB input impedance of 1.5 k $\Omega$  is chosen to be large compared to the 50  $\Omega$  output resistor of the LM to both avoid the factor of two loss in amplitude resulting from a low impedance, and reduce the effects of unavoidable variations in the LM output resistance due to ASIC production process variations.

The gains of the S8x2, S4x4, and S2x8 LSBs are all unity. The S1x16 LSBs are made in three different types: high gain H (g=2 for the HEC and the presampler), low gain L (g=1 for the HEC and the front EMEC section) and mixed gain M (g=1 or g=2 on different channels, used only in the HEC). In the FCAL, weighted sums are used, to account for relatively large variations in the value of sin  $\theta$  over the bins of width  $\Delta \eta = 0.4$ . In addition to their nominal gains, all boards require a

Figure 16. Schematic diagram of the circuits used in the LSBs. For more details, see the text.

small (3%) additional gain to compensate for the voltage reduction caused by the presence of the 50  $\Omega$  series resistor at the LM output.

The amplifier chip chosen for the LSBs is the Intersil HFA1135A [32], a fast current feedback amplifier produced using a bipolar technology. This device is relatively radiation tolerant, and contains voltage limiting circuitry which is needed for rapid and accurate recovery from saturated pulses. The maximum input common mode voltage of the amplifier is important for the low gain single stage amplifier of figure 16(b), as both inputs to the amplifier ride to the maximum level of the pulse. Since the specification for this voltage is 1.7 V for the HFA1135A and the maximum amplitude of the LM output is 3.0 V, the input pulse is attenuated by a factor of two, and the gain of the amplifier is set to two to achieve an overall gain of unity. This precaution is unnecessary for the high gain version of figure 16(a), as the voltage clamp is operational whenever the input is outside the operating range of the IC. In the two-stage circuit of figure 16(c), the resistors used in feedback are 1.5 k $\Omega$  to yield unity gain. To reduce the noise, the resistors of the second stage are chosen to be the lowest values recommended by the manufacturer.

The largest source of noise for the two-stage LSBs is the non-inverting input noise current density of the HFA1135A in the first stage. The specified value [32] of 20 pA/ $\sqrt{\text{Hz}}$ , combined with the 1.5 k $\Omega$  input resistance, yields a noise voltage density of 30 nV/ $\sqrt{\text{Hz}}$  at the output. The bandwidth of the system, measured to be 12 MHz, is limited by the long cables over which the signals are sent to reach the counting room, yielding a noise level of approximately 100  $\mu$ V for this particular source. Measured values of noise at the LSB output range from 140  $\mu$ V for the S2x8 LSB to 200  $\mu$ V for the S8x2 LSB. The noise for the single stage configurations is lower, with measured

**Table 9.** Acceptance criteria applied during testing of the LSBs. The breakpoint voltages are defined as the absolute values of  $V_{out}$  at the upper and lower transitions between the linear and saturation regions of the DC response curve.

| Parameter                            | Acceptance Window |

|--------------------------------------|-------------------|

| Deviation of gain from nominal value | < 2%              |

| Integral nonlinearity                | < 0.7%            |

| DC offset                            | < 40 mV           |

| DC gain in both saturation regions   | < 0.15            |

| Breakpoint voltages                  | 3.2 - 3.8 V       |

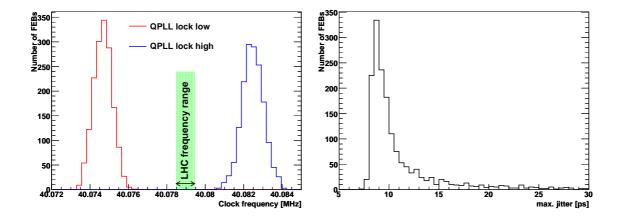

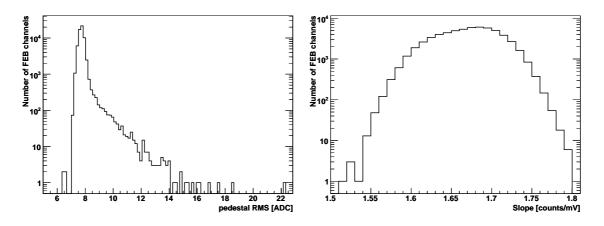

values of 20  $\mu$ V and 42  $\mu$ V for the high and low gain circuits respectively. In the L1 energy scale, 200  $\mu$ V corresponds to 20 MeV of transverse energy, approximately the preamp noise of a single calorimeter cell at  $\eta = 0$ . A complete trigger tower, which is the sum of approximately 60 cells, has preamp noise of about 300 sin  $\theta$  MeV and electronic noise from the four LSBs (one per depth layer) of 30 to 40 MeV. Other sources of electronic noise in the chain (principally the Receiver module, with a variable-gain amplifier) contribute additional noise at the level of 100 MeV.